# 1 MASKING TO EXTRACT PART OF A WORD OF I.A.S.

Word 19 of block 14 contains unwanted data in positions 1 to 6, the data in position 7 to 12 is required in Register B.

Instruction

|     | D | F  | A    | R  |        |

|-----|---|----|------|----|--------|

| ×   |   | 37 | 0019 | 14 | - dalo |

|     | _ | 35 | 0021 | 16 | - mon  |

| X+1 |   |    |      |    |        |

Only the matching binary digits for each position arrive in Register B.

# 2 MASKING TO EXTRACT AN ADDRESS

Mask constants can be used to extract the address from an instruction. An example of this use would be where the instruction tests an indicator, as in this case the address has 4000 added to it. The 4000 can be subsequently removed by using a mask as below

either 0 0 3 151515 0 0 0 0 0 0

depending on whether the instruction to be masked is in the most-significant or least-significant half of the word.

0 0 0 0 0 0 0 0 3 15 15 15

or

### ODD/EVEN NUMBER DISCRIMINATION

A mask can be used to determine whether a number is odd or even. Here word 17 block 19 is examined, the mask being word 14 block 13.

Instruction

| ı   | D | F. | A    | R   |

|-----|---|----|------|-----|

| х   |   | 60 | 0014 | 13_ |

|     |   | 35 | 0017 | 19  |

| X+1 |   |    |      |     |

|     |   |    |      | 1   |

Before

After

| I.A.S. 14 Block 13 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

|--------------------|---|---|---|---|---|---|---|---|---|---|---|---|

| I.A.S. 17 Block 19 |   | 1 |   |   |   |   |   | 5 | 2 | 3 | 8 | 3 |

| Register A         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Register B         | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 8 | 9 | 2 | 3 | 4 |

I.A.S. 17 Block 19 Register A

Register B

I.A.S. 14 Block 13 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 6 5 2 0 0 0 0 0 0 6 5 2 3 8 3 00

At the conclusion of the 35 instruction, it will be possible to discriminate between the presence or absence of a 1-bit by means of Mill Indicators 01 and 02 (see page 54). In the example above indicator 02 is set, as Register B contains a 1-bit corresponding to the I.A.S. contents being odd. If the contents of Register B are zero corresponding to the I.A.S. contents being even, Mill Indicator 01 is set.

During the execution of function 35 the overflow indicator is inhibited but the other Mill Notes Indicators function normally.

# Function 36

2.6.2

Causes the operation of Logical OR to be carried out between the contents of Register Effect B and the contents of a specified location of I.A.S. on a bit-for-bit basis.

A number held in the specified I.A.S. location is put in Register A. Logical OR of the contents of Registers A and B then takes place and the result is placed in Registers A and B and in the original I.A.S. location specified in the instruction.

Examples If 123456123456 is contained in I.A.S. 15 block 12 and 999999666666 is contained in Register B, then at the completion of function 36 the Registers A, B and I.A.S. 15 block 12 will stand thus:

> I.A.S. Register A Register B

| 9 | 11 | 11 | 13 | 13 | 15 | 7 | 6 | 7 | 6 | 7 | 6 |

|---|----|----|----|----|----|---|---|---|---|---|---|

| 9 | 11 | 11 | 13 | 13 | 15 | 7 | 6 | 7 | 6 | 7 | 6 |

| 9 | 11 | 11 | 13 | 13 | 15 | 7 | 6 | 7 | 6 | 7 | 6 |

A study of the 1, 2, 4 and 8 streams of the original contents of word 15 block 12 and Register B, together with the result obtained after Logical OR are shown below:-

Register B

Word 15 Block 12 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 0 1 0 0 1 1 1 0 0 0 1 1 1

0 0 0 0 0 0 1 2 0 0 0 0 0 0 1

Result in Word 15 1 1 0 0 1 Block 12 and 0 1 1 1 1 1 1 2 Registers A and B 0 0 0 1 1 1 1 1 1 1 1 1 4

The most common use for Logical OR is for modifying an instruction by the insertion of an address without using the Mill and in consequence not setting the overflow indicator. For example to modify the first instruction contained in word 12 of block 23 by inserting an address from word 29 of block 21.

Instructions

|     | D | F  | A    | R   |

|-----|---|----|------|-----|

| ×   |   | 37 | 0029 | 21_ |

|     |   | 35 | 0011 | 23  |

| X+1 |   | 36 | 00/2 | 23  |

|     |   |    |      |     |

|                    |   |   |   |    | E  | ef | or | e |   |   |   |   |   |

|--------------------|---|---|---|----|----|----|----|---|---|---|---|---|---|

| I.A.S. 29 Block 21 | 0 | 0 | 1 | 2  | 4  | 8  | 0  | 0 | 0 | 4 | 1 | 9 | Ι |

| I.A.S. 11 Block 23 | _ | _ | 3 | 15 | 15 | 15 | 0  | 0 | 0 | 0 | 0 | 0 | Ι |

| I.A.S. 12 Block 23 | 6 | 0 | 0 | 0  | 0  | 0  | 6  | 3 | 1 | 1 | 9 | 2 | Ι |

|                    |   |   |   |    |    |    |    |   |   |   |   |   |   |

| Register A         | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | R |

| Register B         | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | R |

|        |    |       |    | _ | _ |   |    | _  | _  | _ |   |   |   |   |   |

|--------|----|-------|----|---|---|---|----|----|----|---|---|---|---|---|---|

| I.A.S. | 29 | Block | 21 | 0 | 0 | 1 | 2  | 4  | 8  | 0 | 0 | 0 | 4 | 1 | 9 |

| I.A.S. | 11 | Block | 23 | 0 | 0 | 3 | 15 | 15 | 15 | 0 | 0 | 0 | 0 | 0 | 0 |

| I.A.S. | 12 | Block | 23 | 6 | 0 | 1 | 2  | 4  | 8  | 6 | 3 | 1 | 1 | 9 | 2 |

After

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|            | - |   |   |   |   |   |   |   |   | 119 |   |   |

|------------|---|---|---|---|---|---|---|---|---|-----|---|---|

| Register A | 6 | 0 | 1 | 2 | 4 | 8 | 6 | 3 | 1 | 1   | 9 | 2 |

| Register B | 6 | 0 | 1 | 2 | 4 | 8 | 6 | 3 | 1 | 1   | 9 | 2 |

|            |   |   |   |   |   |   |   |   |   |     |   |   |

The same result can be achieved without using Logical OR. Whereas there is little difference in the time, this second method affects the overflow indicator.

The instructions would be

|                                         | D | F  | A    | R  |

|-----------------------------------------|---|----|------|----|

| ×                                       |   | 37 | 0029 | 21 |

| .,                                      |   | 35 | 0011 | 23 |

| X+1                                     |   | 64 | 0012 | 23 |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |   |    |      |    |

The uses of modifications are discussed in Part 4.

Notes As function 36 does not use the Mill, no Mill Indicators are set by this function.

### ROW BINARIZING

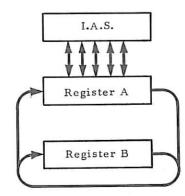

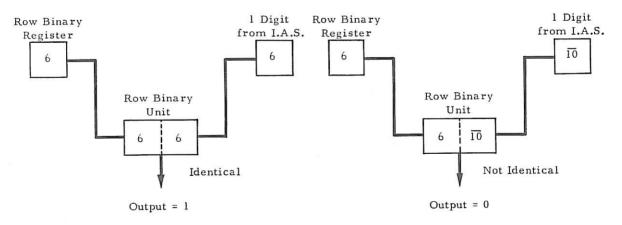

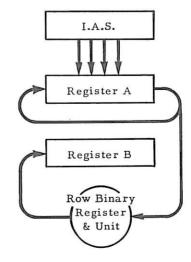

Row-binary is normally created prior to print or punch output as described in Part 3. The components used to create row-binary are Register B, the specified word of I.A.S. and the Row Binary Register together with the Row Binary Unit. As illustrated schematically the Row Binary Register is a single-digit register capable of holding any number from 0 to 15, and the Row Binary Unit uses a technique similar to the Logical AND described in 2.6 but performing the logic on whole digits rather than bits. If a digit from a single position of an I.A.S. location is compared in the Row Binary Unit with the digit in the Row Binary Register, when the digits are identical a 1-bit will be emitted from the output of the device.

According to the function given, the 1s or 0s from the output of the Row Binary Register component can be directed to the appropriate stream of the B Register.

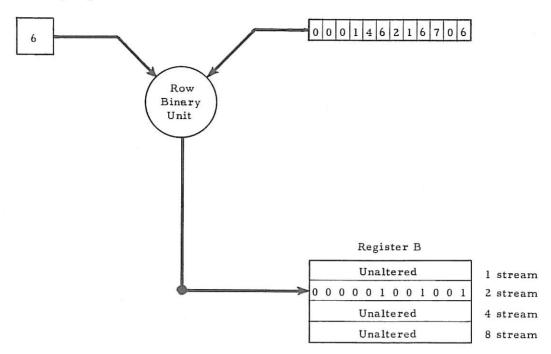

Thus in row binarizing each *digit* of the contents of the specified location of I.A.S. is compared against the digit set in the Row Binary Register. If the digits correspond then a 1-bit is emitted into the appropriate stream of Register B and if the digits fail to correspond a 0 is emitted into the stream of Register B e.g. the Row Binary Register is set to 6 and the instruction is given to create row-binary in stream 2 of Register B for I.A.S. 12 block 11 which contains 000046216706.

2.7

The Row Binary Register can be loaded in one of two ways:

- (a) with the least-significant digit of the contents of a specified location of I.A.S. (see function 30 below).

- (b) with the contents of the index point (print) counter. This method is described in Part 3.

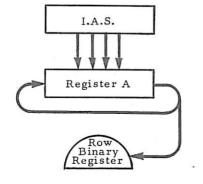

# Function 30 2.7.1

Effect Causes the contents of the least-significant position of a specified location of I.A.S. to be transferred to the Row Binary Register.

**Operation** A number held in the I.A.S. location specified is put in Register A, the least -significant digit being placed in the Row Binary Register. The eleven most-significant figures do not affect the Row Binary Register. At the conclusion of the instruction the contents of Register A will be the original I.A.S. word. The I.A.S. word is unaltered.

Example Transfer 6 contained in the least-significant position of word 19 block 12 to the Row Binary Register.

| Instruction | D | F  | A    | R         |

|-------------|---|----|------|-----------|

|             |   | 30 | 0019 | <u>12</u> |

|             |   |    |      |           |

|                     |   |   |   |   | E | 3ef | for | ·e |   |   |   |   |                     |   |   |   |   | 4 | ₹ft | er | 9 |   |   |   |   |

|---------------------|---|---|---|---|---|-----|-----|----|---|---|---|---|---------------------|---|---|---|---|---|-----|----|---|---|---|---|---|

| I.A.S.              | 3 | 7 | 0 | 1 | 4 | 5   | 6   | 2  | 0 | 3 | 9 | 6 | I.A.S.              | 3 | 7 | 0 | 1 | 4 | 5   | 6  | 2 | 0 | 3 | 9 | 6 |

| Register A          | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0  | 0 | 0 | 0 | 0 | Register A          | 3 | 7 | 0 | 1 | 4 | 5   | 6  | 2 | 0 | 3 | 9 | 6 |

| Row Binary Register |   |   |   |   |   |     |     |    |   |   |   | 8 | Row Binary Register |   |   |   |   |   |     |    |   |   |   | L | 6 |

Notes Sometimes a constant can be found in the program with a digit, in the least-significant position of the second address, suitable to load the Row Binary Register. If, however, none is available it is necessary to create a special constant.

Care must be exercised while programming to ensure that the least-significant digit of the chosen constant is that of the *absolute* Address and not the Relative Address and also that the constant is in I.A.S. when function 30 is obeyed. It is safer to use either a constant or an instruction with no relativizer (e.g. those used to set the Decimal Point or Sterling Position Registers) as these will not change if the storage allocation is altered.

Function 3 2.7.2

Effect Creates row-binary into the 1 stream of Register B for the contents of a specified location of I.A.S.

Operation A number held in the specified I.A.S. location is put in Register A and each digit compared with the digit held in the Row Binary Register. When the digits correspond then a 1-bit is emitted into the 1 stream of Register B, when the digits do not correspond then a 0-bit is emitted into the 1 stream of Register B. At the conclusion of the instruction the contents of the 2, 4 and 8 streams of Register B and the original I.A.S. word are unaltered. Also the contents of Register A will be the original I.A.S. word.

Example 1 Create row-binary into the 1 stream of Register B for the contents of I.A.S.42 block 15. The Row Binary Register contains a 6.

|                      | 31 0042 15                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                     |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Before                                                                                                                                                                                                                                                                                         | Aiter                                                                                                                                                                                                                               |

| I.A.S.<br>Register A | 4       9       6       2       6       0       4       6       9       2       6       6         3       7       0       2       1       9       6       2       0       0       0       3       Register A                                                                                   | 4       9       6       2       6       0       4       6       9       2       6       6         4       9       6       2       6       0       4       6       9       2       6       6                                         |

| Register B           | 0       1       0       0       1       1       0       0       1       0       0       1       Register B         0       0       1       0       1       1       0       0       1       0       1       2         0       1       1       0       0       0       1       1       0       4 | 0     0     1     0     1     0     0     1     0     0     1     1       0     0     1     0     1     1     1     0     1     0     0     1     1     2       0     1     1     0     0     0     1     0     1     1     0     4 |

| Row Binary Regis     | 1 0 0 1 0 0 0 0 0 0 1 8<br>ter 6 Row Binary Regis                                                                                                                                                                                                                                              | 1 0 0 1 0 0 0 0 0 0 0 1 8<br>ster 6                                                                                                                                                                                                 |

Functions 30 to 34 will generally be used for output only, but row-binary techniques can occasionally be used as alternatives to conventional methods of programming in order to save space and/or time.

30

Example 2 Examine word 17 of block 15 for the presence of digit 3 in position 9.

Instruction

|                    |     |   |   |   |   |    | - 6- | _ | _  |     | _ | _ |    |        | <u> </u> |        |       |    |   |      |     |      |               |   |   |   |   |   |   |

|--------------------|-----|---|---|---|---|----|------|---|----|-----|---|---|----|--------|----------|--------|-------|----|---|------|-----|------|---------------|---|---|---|---|---|---|

|                    |     |   |   |   |   |    |      | , | (+ | - 1 |   |   | 35 | _004   | 9        | 19_    |       |    |   |      |     |      |               |   |   |   |   |   |   |

|                    |     |   |   |   |   |    | L    |   |    |     |   |   |    |        |          |        |       |    |   |      |     |      |               |   |   |   |   |   |   |

|                    |     |   |   |   | В | ef | or   | e |    |     |   |   |    |        |          |        |       |    |   |      |     | Ai   | te            | r |   |   |   |   |   |

| I.A.S. 17 Block 15 | 0   | 0 | 0 | 3 | 8 | 3  | 2    | 4 | 3  | 9   | 2 | 6 |    | I.A.S. | 17       | Block  | 15    | 0  | 0 | 0    | 3   | 8 3  | 2             | 4 | 3 | 9 | 2 | 6 |   |

| I.A.S. 41 Block 19 | 0   | 0 | 0 | 0 | 8 | 3  | 2    | 6 | 2  | 4   | 0 | 3 | 1  | I.A.S. | 41       | Block  | 19    | 0  | 0 | 0    | 0   | 8 3  | 2             | 6 | 2 | 4 | 0 | 3 |   |

| I.A.S. 49 Block 19 | 0   | 0 | 0 | 0 | 0 | 0  | 0    | 0 | 1  | 0   | 0 | 0 |    | I.A.S. | 49       | Block  | 19    | 0  | 0 | 0    | 0   | 0 0  | 0             | 0 | 1 | 0 | 0 | 0 |   |

| Register A         | 0   | 0 | 0 | 0 | 0 | 0  | 0    | 0 | 0  | 0   | 0 | 0 |    |        |          |        |       | _  |   | - 1  |     | _    | _             |   |   |   |   | _ |   |

| Register B         | 0   | 0 | 0 | 0 | 0 | 0  | 0    | 0 | 0  | 0   | 0 | 0 |    | Regist | ter      | A      |       | 0  | 0 | 0 10 | ) [ | 0 0  | 0             | 0 | 1 | 0 | 0 | 0 |   |

| Row Binary Registe | e r |   |   |   |   |    |      |   |    |     |   | 0 |    | Regist | ter      | В      |       | 0  | 0 | 0 0  | ) ( | 0    | 0             | 0 | 1 | 0 | 0 | 0 | 1 |

| , ,                |     |   |   |   |   |    |      |   |    |     | ٠ |   |    |        |          |        |       | 0  | 0 | 0 0  | 0   | 0    | 0             | 0 | 0 | 0 | 0 | 0 | 2 |

|                    |     |   |   |   |   |    |      |   |    |     |   |   |    |        |          |        |       | 0  | 0 | 0 0  | 0   | 0    | 0             | 0 | 0 | 0 | 0 | 0 | 4 |

|                    |     |   |   |   |   |    |      |   |    |     |   |   |    |        |          |        |       | 0  | 0 | 0 0  | 0   | 0    | 0             | 0 | 0 | 0 | 0 | 0 | 8 |

|                    |     |   |   |   |   |    |      |   |    |     |   |   |    | Row B  | ina      | ry Reg | giste | er |   |      |     | 2000 | - C. A. VIENE |   |   |   |   | 3 |   |

By examining Mill Indicators 01 and 02, as described under Section 2.6.1 Example 3 Odd/Even Discrimination, it is possible to jump to the section of the program relating only to digit 3 in position 9 of word 17 of block 15.

Example 3 Examine word 49 of block 22 for the presence of digit 6 in position 4, 7 or 11.

Instruction

| I     | D | F  | A    | R  |

|-------|---|----|------|----|

| х     |   | 30 | 0039 | 14 |

|       |   | 31 | 0049 | 22 |

| X + 1 |   | 35 | 0040 | 14 |

|                                                                | Before      |   |          |   |             |   |       |       |       |       |       |     |     | After                                                                                                                            |   |     |

|----------------------------------------------------------------|-------------|---|----------|---|-------------|---|-------|-------|-------|-------|-------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------|---|-----|

| I.A.S. 39 Block 14<br>I.A.S. 40 Block 14<br>I.A.S. 49 Block 22 | 0<br>0<br>0 | 0 | 0        | 1 | 0<br>0<br>6 | 0 | 0 1 7 | 0 0 1 | 0 0 2 | 0 0 8 | 0 1 6 | 0 9 |     | I.A.S. 39 Block 14 0 0 0 0 0 0 0 0 0 0 0 0 0 1 I.A.S. 40 Block 14 0 0 0 1 0 0 1 0 0 0 1 I.A.S. 49 Block 22 0 1 2 6 6 5 7 1 2 8 6 | - |     |

| Register A                                                     | 0           | 0 | 0        | 0 | 0           | 0 | 0     | 0     | 0     | 0     | 0     | 0   |     | Register A 0 0 0 1 0 0 1 0 0 0 1                                                                                                 | 0 |     |

| Register B                                                     | 0           |   | $\dashv$ |   | -           | 0 | -     | 0     | 0     | 0     | 0     | -   | 1 2 | Register D                                                                                                                       |   | 1 2 |

|                                                                | 0           | 0 | 0        | 0 | 0           | 1 | 0     | 0     | 1     | 0     | 1     | 1   | 4   | 0 0 0 0 0 0 0 0 0 0 0                                                                                                            | 0 | 4   |

|                                                                | 0           | 1 | 0        | 1 | 0           | 0 | 0     | 0     | 0     | 1     | ò.    | 0   | 8   | 0 0 0 0 0 0 0 0 0 0 0                                                                                                            | 0 | 8   |

| Row Binary Regist                                              | er          |   |          |   |             |   |       |       |       |       |       | 0   |     | Row Binary Register                                                                                                              | 6 |     |

By examining Mill Indicators 01 and 02, as described under Section 2.6.1 Example 3 Odd/Even Discrimination, it is possible to jump to the section of the program relating only to instances where a 6 appears in position 4, 7 or 11 of word 49 of block 22.

Note No Mill Indicators are set by function 31 as the Mill is not involved in the operation.

# Function 32 2.7.3

Function 32 creates row-binary into the 2 stream of Register B for the contents of a specified word of I.A.S. in the manner described in 2.7.2.

# Function 33 2.7.4

Function 33 creates row-binary into the 4 stream of Register B for the contents of a specified word of I.A.S. in the manner described in 2.7.2.

# Function 34 2.7.5

Function 34 creates row-binary into the 8 stream of Register B for the contents of a specified word of I.A.S. in the manner described in 2.7.2.

Examine word 16 of block 21 for the presence of digit 3, 6, 7 or 8 in positions 11 or 12.

Instruction

|     | D | F  | Α    | R  |

|-----|---|----|------|----|

| ×   |   | 30 | 0039 | 19 |

|     | L | 31 | 0016 | 21 |

| x+1 |   | 30 | 0040 | 19 |

|     |   | 32 | 0016 | 21 |

| x+2 |   | 30 | 0041 | 19 |

|     |   | 33 | 0016 | 21 |

| x+3 |   | 30 | 0042 | 19 |

|     |   | 34 | 0016 | 21 |

| x+4 |   | 35 | 0043 | 19 |

|     |   |    |      |    |

|                    |    |   |     | 33  | Be: | foi | ·e |   |   |    |    |    |      |       |            |         |     |   |   |   | 1 | Aft | er |          |        |   |    |     |   |

|--------------------|----|---|-----|-----|-----|-----|----|---|---|----|----|----|------|-------|------------|---------|-----|---|---|---|---|-----|----|----------|--------|---|----|-----|---|

| I.A.S. 39 Block 19 | 8  | 4 | 0   | 1 2 | 7   | 9   | 1  | 5 | 8 | 6  | 13 | 3  | I.A. | 5. 39 | 9          | Block 1 | 9 8 | 4 | 0 | 4 | 2 | 7   | 9  | 1        | 5      | 8 | 6  | 3   |   |

| I.A.S. 40 Block 19 | 5  | 7 | 9   | 1 3 | 6   | 2   | 8  | 0 | 5 | 4  | 6  |    | I.A. | 5.40  | 0          | Block 1 | 9 5 | 7 | 9 | 1 | 3 | 6   | 2  | 8        | 0      | 5 | 4  | 6   |   |

| I.A.S. 41 Block 19 | 3  | 7 | 7   | 7 5 | 1   | 9   | 6  | 1 | 2 | 4  | 7  | 7. | I.A. | 5.4   | 1          | Block 1 | 9 3 | 7 | 7 | 7 | 5 | 1   | 9  | 6        | 1      | 2 | 4  | 7   |   |

| I.A.S. 42 Block 19 | 3  | 2 | 4 8 | 3 4 | 6   | 4   | 2  | 7 | 1 | 1  | 8  | 3  | I.A. | 5. 42 | 2 :        | Block 1 | 9 3 | 2 | 4 | 8 | 4 | 6   | 4  | 2        | 7      | 1 | 1  | 8   |   |

| I.A.S. 43 Block 19 | 0  | 0 | 0 ( | 0   | 0   | 0   | 0  | 0 | 0 | 15 | 1  | 5  | I.A. | 5. 43 | 3 :        | Block 1 | 9 0 | 0 | 0 | 0 | 0 | 0   | 0  | 0        | 0      | 0 | 15 | 15  |   |

| J.A.S. 16 Block 21 | 0  | 0 | 7 9 | 9 6 | 5   | 8   | 9  | 2 | 4 | 3  | 8  | 3  | I.A. | 5. 16 | <b>5</b> ] | Block 2 | 1 0 | 0 | 7 | 9 | 6 | 5   | 8  | 9        | 2      | 4 | 3  | 8   |   |

| Register A         | 0  | 0 | 0 0 | 0 0 | 0   | 0   | 0  | 0 | 0 | 0  | C  |    | Regi | stei  | r.         | A       | 0   | 0 | 0 | 0 | 0 | 0   | 0  | 0        | 0      | 0 | 5  | . 5 |   |

|                    |    |   |     |     |     |     |    |   |   |    |    |    | Regi | stei  | r ]        | В       | 0   | - | 0 | 0 |   |     |    | 0        |        | 0 | -  | 0   | 1 |

|                    |    |   |     |     |     |     |    |   |   |    |    |    |      |       |            |         | 0   |   | 0 |   |   | +   | 7  | $\dashv$ |        | 0 | 0  | 0   | 2 |

| Register B         | 0  | 0 | مآه | 0 0 | 0   | 0   | ^  | 0 | 0 | 0  |    | П  |      |       |            |         | 0   | _ |   |   | 7 | _   |    | +        | $\neg$ |   | +  | 0   | 4 |

| -                  |    | U | υį  | 10  | 10  | U   | 0  | U | U | 0  | -  | 4  |      |       |            |         | 0   | 0 | 0 | 0 | 0 | 0   | 0  | 0        | 0      | 0 | 0  | 1   | 8 |

| Row Binary Registe | er |   |     |     |     |     |    |   |   |    | 0  |    | Row  | Bina  | ır         | y Regis | ter |   |   |   |   |     |    |          |        |   |    | 8   |   |

By testing Mill Indicators 01 and 02, as described under Section 2.6.1 Example 3 Odd/Even Discrimation, it is possible to jump to the section of the program relating only to instances where a 3, 6, 7 or 8 appears in positions 11 or 12 of word 16 of block 21.

### SHIFT INSTRUCTIONS

2.8.

Data in Register B can be moved en bloc to right or left within the register. This technique known as shifting is used to move numbers beyond the capacity of Register B so that they are either eliminated or circulated, that is, they re-enter Register B at the opposite end.

Generally a simple problem of extraction of a part of a word can be solved by the shifting method, using less storage though taking slightly more time than the masking method using Logical AND (see 2.6.1). This is because the latter case requires storage for a special masking constant.

However, a more complicated problem of this type, for example the extraction of positions 1 to 3 and 6 to 9 of a word is more economically solved by the mask constant method both in time and storage required. The method to be preferred will depend on the relative necessity of economizing on time or storage in the rest of the program.

The number of positions shifted is determined by the number in the two least-significant positions of the address part of the instruction which may take any value from 00 to 12. As far as the shift instruction itself is concerned, it is immaterial whether the contents of Register B are in decimal or sterling form. However, when a sterling amount is shifted to a different position in Register B it is necessary to set the Sterling Position Register (see 2.4.1) to correspond to the new tens of shillings position before applying any of the sterling arithmetic functions (i.e. functions 70 to 79) to the contents of Register B.

The shift functions do not send the contents of Register B through the Mill, and therefore cannot set any of the Mill Indicators.

A relativizer should not be used with a shift instruction, otherwise the address part of the instruction which specifies the number of positions to be shifted will be mutilated.

Function 54 2.8:1

Effect Causes the contents of Register B to be circulated to the left.

**Operation** A number held in Register B is effectively shifted n places to the left of its original position; n is determined by the number (between 00 and 12) in the two least-significant positions of the address part of the instruction. Those digits which move out of the most-significant position re-enter Register B at the least-significant position.

It is actually only possible to perform a right shift in Register B. Function 54 is therefore effected by a right shift of that number of places which achieves the same result as the specified left shift.

Register B

Example Circulate the contents of Register B five places to the left.

Register B 0 1 2 3 4 5 6 7 8 9 10 1 1

Before

Register B

5 6 7 8 9 10 11 0 1 2 3 4

After

45

Function 55

Effect Causes the contents of Register B to be shifted to the left, entering zeros in the least -significant position.

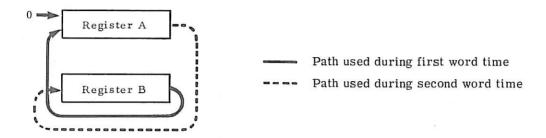

Operation This function operates over two word times and unlike other shift functions utilizes Register A. This is necessary to achieve the specified left shift, which must in fact be performed as two right shifts. During the first word time Register A is zeroized and the digits which are to remain in the result are shifted from Register B into the most-significant end of Register A. During the second word time the contents of Register A are circulated into Register B to achieve the required result. Register A contains zeros on completion of the instruction.

Example Shift the contents of Register B six places to the left and fill the vacated positions with zeros.

| 55 | 0006 |         |

|----|------|---------|

|    | 55   | 55 0006 |

|            | Before                   |            | After                     |

|------------|--------------------------|------------|---------------------------|

| Register A | 0 0 0 0 0 0 0 1 2 3 4 5  | Register A | 0 0 0 0 0 0 0 0 0 0 0 0   |

| Register B | 1 2 4 3 6 7 910 5 8 11 4 | Register B | 9 10 5 8 11 4 0 0 0 0 0 0 |

Note As this function takes longer to execute than function 54, wherever possible function 54 should be used in preference to function 55.

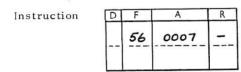

Function **56** 2.8.3

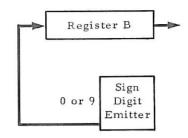

Effect Causes the contents of Register B to be shifted to the right, entering either 0s or 9s in the most-significant position according to the value of the original digit in the most-significant position.

Operation A number held in Register B is shifted n places to the right of its original position: n is determined by the number (between 00 and 12) in the two least-significant positions of the address part of the instruction.

Those most-significant positions vacated are filled with either zeros if the original digit in the most-significant position was from 0 to 4, or nines if the original digit in the most-significant position was from 5 to 15. Thus the most-significant position is regarded as the sign position, 0 to 4 indicating a positive figure, 5 to 15 a negative figure.

### Examples

Before

After

(a) Shift the contents of Register B five places to the right and fill the vacated positions with eight zeros if 0 to 4 is in position 1 of Register B or nines if 5 to 15 is in position 1 of Register B.

| Register B               |    |        | Register B              |

|--------------------------|----|--------|-------------------------|

| 0 1 2 3 4 5 6 7 8 9 1011 | or | Before | 9 9 1 2 3 4 5 0 0 0 0 0 |

After

(b) Shift the contents of Register B seven places to the right, propagating the sign.

Instruction

0 0 0 0 0 0 1 2 3 4 5 6

Instruction

(c) Shift the contents of Register B twelve places to the right, propagating the sign.

|        | <del></del>              |    |        |                         |

|--------|--------------------------|----|--------|-------------------------|

|        | Register B               |    |        | Register B              |

| Before | 10 0 0 0 0 0 0 0 4 3 2 1 | or | Before | 4 6 0 0 0 0 1 2 3 4 5 6 |

| After  | 9 9 9 9 9 9 9 9 9 9 9    |    | After  | 0000000000000           |

Effect Causes the contents of Register B to be shifted to the right, entering zeros in the most -significant position.

**Operation** A number held in Register B is shifted n places to the right of its original position; n is determined by the number (between 00 and 12) in the two least-significant positions of the address part of the instruction. The most-significant positions vacated are filled with zeros.

### Examples

(a) Shift the contents of Register B five places to the right, do not propagate the sign.

Instruction

| D | F  | Α    | R |        |   |   |   | R | eg | is | teı | : B | 3 |     |     |   |

|---|----|------|---|--------|---|---|---|---|----|----|-----|-----|---|-----|-----|---|

|   | 57 | 0005 |   | Before | 0 | 1 | 2 | 3 | 4  | 5  | 6   | 7   | 8 | 9 1 | 01  | 1 |

| _ |    |      |   | After  | 0 | 0 | 0 | 0 | 0  | О  | 1   | 2   | 3 | 4   | 5 6 | , |

(b) Shift the contents of Register B seven places to the right, do not propagate the sign.

Instruction

| D | F  | Ä    | R |        |   |   |   | F | leg | gis | te | r I | 3 |   |   |   |

|---|----|------|---|--------|---|---|---|---|-----|-----|----|-----|---|---|---|---|

|   | 57 | 0007 |   | Before | 6 | 5 | 4 | 3 | 2   | 1   | 6  | 5   | 4 | 3 | 2 | l |

|   |    |      |   | After  | 0 | 0 | 0 | 0 | 0   | 0   | 0  | 6   | 5 | 4 | 3 | 2 |

### Application of the Shift Functions

2.8.5

- (a) Zeroizing Register B. Instruction 570012 is the most economical method.

- (b) Extraction of part of a word: It is sometimes more economical in time or space or both to use shift functions in preference to Logical AND with a mask constant (described under 2.6.1). In the following examples, (i) the Shifting Method is more economical on storage, (ii) the Mask Constant Method is more economical on time.

Extract from word 25 of block 35 the quantity held in positions 9 to 12 and place it in word 26 of block 35.

(i) Shifting Method.

Instruction

| D | F  | A    | R        |

|---|----|------|----------|

|   | 37 | 0025 | 35       |

|   | 54 | 0008 | <u> </u> |

|   | 57 | 0008 |          |

|   | 42 | 0026 | 35       |

|   |    |      |          |

|   |    |      |          |

#### Before

| Word 25 Block 35 | 1 | 2 | 3 | 0 | 1 | 10 | 4 | 6 | 3 | 2 | 1 | 9 |

|------------------|---|---|---|---|---|----|---|---|---|---|---|---|

| Word 26 Block 35 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 |

| Register A       | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 |

After

|                  |   | _ |

|------------------|---|---|

| Word 25 Block 35 | 1 | 2 |

| Word 26 Block 35 | 0 | 0 |

| Register A       | 0 | 0 |

| _ |   | _ |   | _ |    | _ | _ |   |   |   |   |

|---|---|---|---|---|----|---|---|---|---|---|---|

| 1 | 2 | 3 | 0 | 1 | 10 | 4 | 6 | 3 | 2 | 1 | 9 |

| 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 3 | 2 | 1 | 9 |

| 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 3 | 2 | 1 | 9 |

Register B

| 1 | _ | _ | ~ | _ | _ | _ | _ | _ | _ | _ | - | _ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Register B

0 0 0 0 0 0 0 0 3 2 1 9

### (ii) Masking Constant Method

Instruction

| D | F  | A    | R  |

|---|----|------|----|

|   | 37 | 0025 | 35 |

|   | 35 | 0006 | 18 |

|   | 42 | 0026 | 35 |

Before

Word 6 Block 18 Word 25 Block 35 Word 26 Block 35 Register A

Register B

|   |   |   |   |   | 1.0 |   |   |    |    |    |    |

|---|---|---|---|---|-----|---|---|----|----|----|----|

| 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 | 15 | 15 | 15 | 15 |

| 1 | 2 | 3 | 0 | 1 | 10  | 4 | 6 | 3  | 2  | 1  | 9  |

| 0 | 0 | 0 | 0 | 0 | o   | 0 | 0 | 0  | 0  | 0  | 0  |

| 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 | 0  | 0  | 0  | 0  |

| 0 | 0 | 0 | 0 | 0 | 0   | 0 | o | 0  | 0  | 0  | 0  |

Word 6 Block 18 Word 25 Block 35 Word 26 Block 35

Register A Register B

| 0 | 0 | 0  | 0 | 0  | 15 | 15 | 15 |

|---|---|----|---|----|----|----|----|

| 0 | 1 | 10 | 4 | 6  | 3  | 2  | 1  |

| 0 | ^ | 0  | ^ | 10 | 2  | 2  | ,  |

| 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 15 | 15 | 15 | 15 |

|---|---|---|---|---|----|---|---|----|----|----|----|

| 1 | 2 | 3 | 0 | 1 | 10 | 4 | 6 | 3  | 2  | 1  | 9  |

| 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 3  | 2  | 1  | 9  |

| 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 3  | 2  | 1  | 9  |

| 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 3  | 2  | 1  | 9  |

After

(c) Shifting the positions of quantities in a word, e.g. for rounding purposes.

Round up quantity held in word 16 block 23. Example I

Instruction

| D | F  | Α    | R  |

|---|----|------|----|

|   | 60 | 0016 | 23 |

|   | 62 | 0010 | 18 |

|   | 56 | 0003 | -  |

|   | 42 | 0016 | 23 |

Before

I.A.S. 10 Block 18 0 0 0 0 0 0 0 0 5 0 0 0 0 0 0 0 0 6 5 2 8 0 0 I.A.S. 16 Block 23 0 0 0 0 0 0 0 0 0 0 0 000

I.A.S. 10 Block 18 I.A.S. 16 Block 23 Register A

Register B

0 0 0 0 0 0 0 0 0 5 0 0 0 0 0 0 0 0 0 0 6 5 3 0 0 0 0 0 0 0 0 0 6 5 3

After

0 0

0 0 0 0 0

Register A

Register B

49

Example 2 Multiply word 129 of block 14 by word 28 block 13. Round up the product to the nearest penny and add the result to the quantity in word 39 block 15.

#### Instruction

|     | D | F               | A            | R               | NARRATIVE                                                         |

|-----|---|-----------------|--------------|-----------------|-------------------------------------------------------------------|

| ×   |   | <i>37 54</i>    | 0129<br>0003 | <u> 14</u> _    | Transfer to Register B  Circulate left 3 positions                |

| X+1 |   | <i>4</i> 2      | 0129         | 14_             | Transfer to original locations  Transfer multiplier to Register B |

| X+2 |   | <u>22</u><br>21 | 0007<br>0003 | 1   1           | Set Sterling Position Register Set Decimal Point Register         |

| X+3 |   | 79<br>72        | 0129         | <u>/4</u><br>32 | Multiply Round up                                                 |

| X+4 |   | 56<br>22        | 0003         | 1   1           | Right Shift 3 positions Reset Sterling Position Register          |

| X+5 |   | 74              | 0039         | 15              | Add to I.A.S.                                                     |

Before

After

Word 28 Block 13 Word 129 Block 14 Word 39 Block 15 Word 16 Block 32 Register B

| 0 | 0 | 0, | 0 | 0 | 0, | 0 | 0 | 0. | 9 | 9 | 9  |

|---|---|----|---|---|----|---|---|----|---|---|----|

| 0 | 0 | 0, | 0 | 0 | 0, | 0 | 0 | 9  | 1 | 9 | 11 |

| 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  |

| 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  | 5 | 0 | 0  |

| 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  |

| Word 28 Block 13 |

|------------------|

| Word 129 Block 1 |

| Word 39 Block 15 |

| Word 16 Block 32 |

| Register B       |

| 0 | 0 | 0, | 0 | 0 | 0, | 0 | 0 | 0. | 9 | 9 | 9 |

|---|---|----|---|---|----|---|---|----|---|---|---|

| 0 | 0 | 0  | 0 | 0 | 9  | 1 | 9 | 11 | 0 | 0 | 0 |

| 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 9  | 1 | 9 | 9 |

| 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 0  | 5 | 0 | 0 |

| 0 | 0 | 0  | 0 | 0 | 0  | 0 | 0 | 9  | 1 | 9 | 9 |

# 'DO NOTHING' AND 'STOP' FUNCTIONS Function 00

2.9

2.9.1

Effect Causes the computer to do nothing and proceed to the next instruction in the normal manner.

Operation The computer obeys the instruction, therefore time is taken in operation but I.A.S. and registers concerning the programmer are in no way affected.

Notes This instruction may be used when it is necessary to modify the other instruction contained in the I.A.S. location. This may be more easily achieved by placing the instruction to be modified in the least-significant part of a location and having a 'do-nothing' instruction in the most -significant part e.g.

|   | D | F  | A    | R  |

|---|---|----|------|----|

| × | _ | 00 | 0012 | 00 |

|   |   | 35 | 0009 | 12 |

The address will usually be zero, but as in the illustration, it may be any number between 0 and 3999.

Function | | 2.9.2

Effect Causes the computer to stop all further operations.

Operation The computer will stop all operations when this instruction is obeyed. If the address positions are used to contain a code number in the range 0 to 3999, after the stop the code number will be displayed on the console in CR3 with one added to it. Normal computer operation will be resumed when the Start button is operated.

Note The code numbers used in the address positions for this instruction can be used to indicate particular reasons for the stop e.g. when a sequence error occurs or an abnormal arithmetic condition is reached.

INDICATORS 2.10

Indicators are devices which may be in either one of two states, set or unset, and are used to direct the program into one of two branches according to the state of the indicator. This is achieved by writing an indicator test instruction. If the indicator is unset, the program proceeds to the normal next instruction. If the indicator is set, the program branches to the instruction pair in the I.A.S. location specified in the address part of the test instruction.

A summary of the characteristics of indicators numbers 00 to 29 is given in tabular form in the table overleaf. All other indicators (numbers 30 to 99) are dealt with in Part 3.

A complete summary of indicators is given in Part 6.

### Representation of an Indicator Test Instruction

2.10.1

Some examples of indicator test instructions are given in Figure 6 (page 53). The first and second positions of the instruction contain the indicator number. The third position must contain a decimal digit whose binary representation contains a 1 in the 4 stream and a 0 in the 8 stream i.e. the number must be 4, 5, 6 or 7. This indicates to the computer that the instruction is a test instruction. The 4-bit is entered into the third position of the instruction during the Initial Orders program. On both the program sheet and the program card, the 4-bit occupies a separate column known as the designation column.

The third, fourth, fifth and sixth positions contain the I.A.S. address of the instruction to which the program will jump if the tested indicator is set. Thus in the case of a computer fitted with more than 1,000 words of I.A.S., following completion of the Initial Orders program, position 3 of the instruction may contain both a 1 and a 4 in binary representation. For a machine with 4,000 words position 3 may also contain a 2-bit.

| Indicator<br>No. | Class of Indicator              | i                  | of Design | nation<br>9 | Set by:-                                                                   | Unset by:-                                   |

|------------------|---------------------------------|--------------------|-----------|-------------|----------------------------------------------------------------------------|----------------------------------------------|

| 00               | Unconditional Jump<br>Indicator | Test               | _         | -           | Permanently set                                                            | -                                            |

| 01               | Mill Indicator                  | Test               | _         | -           | Last no. through<br>Mill zero.                                             | Last no. through<br>Mill not zero.           |

| 02               | Mill Indicator                  | Test               | -         |             | Last no. through<br>Mill > 0 (sign<br>digit 0-4)                           | Last no. through<br>Mil1≤ 0                  |

| 03               | Mill Indicator                  | Test               | _         | _           | Last no. through<br>Mill < 0 (sign<br>digit 5-9)                           | Last no. through<br>Mill≥0                   |

| 04               | Error Indicator                 | Test<br>&<br>Unset | -         | -           | Overflow (sign<br>digit 1-8 or sign<br>digit 9 & all<br>other digits zero) | Program when tested                          |

| 06               | Error Indicator                 | Test<br>&<br>Unset | æ         | -           | I.A.S. Parity<br>Check Error                                               | Program when tested                          |

| 07               | Error Indicator                 | Test<br>&<br>Unset | -         | -           | Drum Parity<br>Check Error                                                 | Program when tested                          |

| 10               | Program Indicators              | Test               | Set       | Unset       | Instruction (Des.8)                                                        | Instruction (Des.9)                          |

| 20               | Manual Indicators               | Test               | -         | -           | Manual Control<br>on Console<br>(Switch on)                                | Manual Control<br>on Console<br>(Switch off) |

### TABLE OF INDICATORS 00 TO 29

An indicator test instruction may form either the first or second half of an instruction word i.e. either positions 1 to 6 or 7 to 12.

| Test instruction as written on program sheet | Form of instruction<br>in computer following<br>Initial Orders program | Significance<br>of<br>instruction                                                                                                            |

|----------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1 D F A R 21 4 03 0037 -                     | 034037                                                                 | Test Indicator 03; if set, jump to I.A.S. 37 (absolute address); if unset proceed to instruction in second half of I.A.S.21.                 |

| 1 D F A R 36 4 15 0106 B                     | 154456                                                                 | Test Indicator 15; if set, jump to I.A.S. 106 of same block; if unset, proceed to instruction in second half of I.A.S. 36 of the same block. |

| Where block relativizer is set to 350        |                                                                        |                                                                                                                                              |

| 1 D F A R 53                                 | 275983                                                                 | Test Indicator 27; if set, jump to I.A.S. 123 block 72 if unset, proceed to instruction in first half of I.A.S. 54 of the same block.        |

| Relativizer for block 72                     |                                                                        |                                                                                                                                              |

Figure 6: EXAMPLES OF INDICATOR TEST INSTRUCTIONS

### Incorrect Test Instructions

is set to 1860

2.10.2

In the case of incorrect test instructions being given to the computer, the sequence of operations is as follows:

If the specified indicator exists, but the I.A.S. address is outside the specifiable range, then; if the indicator is unset, the computer will proceed in the normal manner to the next instruction; if the indicator is set, the computer will stop with zeros in control registers 1 and 2, and the "I.A.S. Check Error on transfer to control register" visual indicator will be set.

If the specified indicator does not exist the computer will proceed in the normal manner to the next instruction.

# Automatic Indicators 2.10.3

Automatic indicators are set, and in some instances unset, by conditions arising in the central processor or in the peripheral units. The conditions arising in the peripheral units are described in Part 3. The other automatic indicators are numbers 00 to 07.

Indicator 00 2.10.4

Purpose Testing indicator 00 causes an unconditional jump to a specified word of I.A.S.

**Operation** This indicator is permanently set. When tested, the next program instruction will not be taken from the next word of I.A.S., but due to the jump, will be taken from the word of I.A.S. specified in the address part of the indicator test instruction.

Example It is required to transfer the contents of I.A.S. location 12 into I.A.S. location 19 if the contents are positive to zero, but to leave the contents of I.A.S. 19 unaltered if the contents of I.A.S. 12 are negative, I.A.S. 12 and 19 being relative addresses in block 17.

| 1    | D | F  | A    | R  | NARRATIVE                                                                       |

|------|---|----|------|----|---------------------------------------------------------------------------------|

| 125  | - | 60 | 00/2 | 17 | Contents of I.A.S. 12, block 17,<br>into Register B via Mill                    |

| , 23 | 4 | 03 | 0127 | B  | Test indicator 03, if set (set on < 0) jump to 1.A.S. 127 of same block         |

| 12 / | - | 42 | 0019 | 17 | If indicator 03 Is not set, write contents of Register B in 1.4.5.19, block 17, |

| 126  | 4 | 00 | 0127 | B  | then jump to 1.A.S. 127 of same block                                           |

Notes An unconditional jump may be usefully employed when it is not possible to use the second half of an I.A.S. location for an instruction. The use of an unconditional jump under these circumstances is preferable to the use of function 00 (Do-nothing instruction) because the former takes less time.

Mill Indicators 2.10.5

The Mill Indicators are indicators 01, 02, 03 and 04. These indicators may be set by any function which involves the transfer of words through the Mill i.e. functions 35, 60 to 69, 70 to 79, except that indicator 04 (the overflow indicator) cannot be set by function 35. A word in this case is regarded as a number up to eleven digits together with a sign digit in the first position.

The Mill Indicators are set by the number which leaves the Mill after completion of the appropriate arithmetical operations within the Mill and not by the numbers entering the Mill.

Indicators 01, 02 and 03 remain set until a number with a different sign results in the Mill. Indicator 04 remains set until it is tested; testing automatically unsets it.

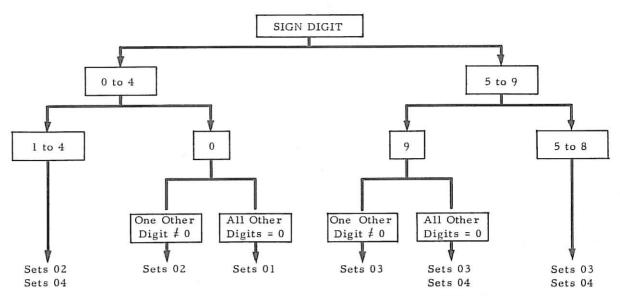

The setting of indicators 01, 02, 03 and 04 is shown diagrammatically in Figure 7.

Figure 8 (page 56) depicts a portion of program in which indicators 01, 02, 03, and 04 are tested. The example assumes that according to the nature of the sum of the contents of I.A.S. locations 20 and 31 (relative addresses in block 10) the following action is required:

- (a) if an overflow occurs, the program must enter an error routine starting at I.A.S. location 80 of the same block of program;

- (b) if the sum of the contents is zero, positive, or negative, a jump is to be made to I.A.S. location 61, 65 or 73 respectively, also in the same block.

The last instruction could equally well be an unconditional jump because if indicators 02 and 03 are both unset, indicator 01 must be set.

Figure 7: SETTING INDICATORS 01, 02, 03, AND 04

Indicator 0 2.10.6

Purpose May be used to test whether the last number resulting in the Mill was zero.

Operation Indicator 01 is set if the entire word is zero, i.e. if the sign digit and all other positions are zero (Figure 7). When indicator 01 is tested and found to be set, a jump is made to the I.A.S. word specified in the address part of the indicator test instruction.

The indicator remains set until a non-zero number results in the Mill.

Example See Figure 8.

Indicator 02 2.10.7

Purpose May be used to test whether the last number resulting in the Mill was positive.

Operation Indicator 02 is set if the word is positive, i.e. either if the sign digit is zero but at least one other digit is greater than zero, or, if the sign digit lies between 1 and 4 inclusive regardless of the state of the rest of the word (Figure 7). When indicator 02 is tested and is found to be set, a jump is made to the I.A.S. word specified in the address part of the indicator test instruction.

The indicator remains set until a negative or zero number results in the Mill.

Example See Figure 8.

Indicator 03 2.10.8

Purpose May be used to test whether the last number resulting in the Mill was negative.

Operation Indicator 03 is set if the word is negative, i.e. if the sign digit lies between 5 and 9 inclusive regardless of the state of the rest of the word (Figure 7). When indicator 03 is tested

55

and is found to be set, a jump will be made to the I.A.S. word specified in the address part of the indicator test instruction.

The indicator remains set until a positive or zero number results in the Mill.

Example See Figure 8.

Indicator 04 2.10.9

Purpose May be used to test whether an overflow has resulted in the Mill since the indicator was last tested.

**Operation** Indicator 04 (overflow indicator) is set if any of the arithmetical functions (functions 60 to 69, 70 to 79) causes either of the following two conditions to result in the Mill:

- (a) a sign digit with a value 1 to 8 inclusive, or

- (b) a 9 in the sign position with zeros in all other positions.

The overflow indicator remains set until it is tested, testing automatically unsets the indicator. Thus by testing the overflow indicator it is possible to detect whether or not an overflow has occurred into the sign position at any time since the indicator was last tested. If two numbers are added or subtracted and the overflow indicator is set, no information will have been lost. If two numbers are multiplied and the overflow indicator is set, information may have been lost.

When indicator 04 is tested and is found to be set, a jump will be made to the I.A.S. word specified in the address part of the indicator test instruction.

#### Example

| I  | D             | F               | Α                   | R               | NARRATIVE                                                                                               |

|----|---------------|-----------------|---------------------|-----------------|---------------------------------------------------------------------------------------------------------|

| 57 | 4             | 04              | 0058                | <br>B           | Test for overflow, to unset indicator                                                                   |

| 58 |               | 60<br>62        | <u>0020</u><br>0031 | <u>10</u><br>10 | Clear Add I.A.S. 20, block 10 to Register B.  Add I.A.S. 31, block 10 to Register B                     |

| 59 | 4             | 0 <u>4</u>      | 0080                | B<br>B          | If overflow indset, jump to I.A.S.80, same block  If ind.02 set (No. 70), jump to I.A.S.65, same block  |

| 60 | <u>4</u><br>4 | <u>03</u><br>01 | 0073<br>0061        | <u>B</u><br>B   | If ind O3set (No < 0), jump to I.A.S.73, same block  If ind O1set (No.=0), jump to I.A.S.61, same block |

Figure 8: EXAMPLE INSTRUCTIONS TESTING INDICATORS 01, 02, 03, AND 04

### Indicator 06 (I.A.S. Check Error Indicator)

2.10.10

Purpose Indicator 06 is used to test whether an I.A.S. transfer parity error has been detected since the indicator was last tested.

Operation An I.A.S. parity check is carried out when a word is transferred from I.A.S. to Register A.

Indicator 06 is automatically set if an I.A.S. parity error is detected on a transfer other than a transfer to the control registers.

Indicator 06 is unset when tested by program.

When the indicator is set the I.A.S. Error lamp on the console glows. If the Optional Stop switch is on, then the computer stops as soon as the parity error is detected. In this case the I.A.S. Error light is extinguished when the computer is restarted but indicator 06 remains set until tested by program.

Notes The computer always stops automatically if an I.A.S. parity error is detected on a transfer to the control registers. The I.A.S. parity checking system is described in more detail in 2.13.1.

The technique for restarting after I.A.S. parity failure is discussed in Part 4.

### Indicator 07 (Drum Check Error Indicator)

2.10.11

Purpose Indicator 07 is used to test whether a drum transfer parity error has been detected since the indicator was last tested.

Operation A drum parity check is carried out when words are transferred from the drum.

Indicator 07 is automatically set if a drum parity error is detected.

Indicator 07 is unset when tested by program.

When the indicator is set the Drum Error lampon the console glows. If the Optional Stop switch is on, then the computer stops as soon as the parity error is detected. In this case the Drum Error light is extinguished when the computer is restarted but indicator 07 remains set until tested by program.

Notes The drum parity checking system is described in more detail in 2.13.2.

The technique for restarting after drum parity failure is discussed in Part 4.

# Programmed Indicators

2.10.12

The ten programmed indicators are indicators 10 to 19. These indicators are identical in operation and are set, unset and tested by means of instructions. The testing will not cause the indicators to be set or unset as a result of the test.

There are ten visual indicators (lamps) on the console, one for each indicator, which show the state of the indicators.

# Indicators 10 to 19

2.10.13

Purpose These indicators are program controlled and are provided so that conditions can be designated and then later differentiated.

57

Operation Indicators 10 to 19 are set by an instruction containing an 8 in the designation position and are unset by a 9 in the designation position. Either of these two designations must be combined with the number of the indicator (10 to 19) in the first and second positions of the instruction. During Initial Orders, the 8 or 9 designation will be placed in the third position of the instruction.

The lamp associated with a particular indicator glows when that indicator is set. The light is extinguished when the indicator is unset.

Example It is required to set indicator 13 if the class of card designation held in position 12 of I.A.S. location 32 (a relative address in block 10) is a 5; (positions 0 to 11 are zeros); the indicator is to be unset later in the program.

#### Instruction

|    | D             | F         | A            | R               | NARRATIVE                                                                                                                                                          |

|----|---------------|-----------|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35 |               | 60        | 0032         | <u>/o_</u>      | Class of card designation transferred to Reg. B                                                                                                                    |

|    | -             | 63        | 0006         | 15              | Subtract '5' held in I.A.S. location 6, block 15                                                                                                                   |

| 36 | <u>4</u><br>4 | 01        | 0037<br>0038 | <u>B</u> _<br>B | Test if ind Olset, i.e. if card designation is 5, if so jump to I.A.S. location 37 of this block If ind Olunset, jump straight to I.A.S. location 38 of this block |

| 37 | 8             | <u>/3</u> | 0038         | <br>B           | If indicator 01 set, set indicator 13  Jump to 1.A.S. location 38 of this block                                                                                    |

|    |               |           |              |                 |                                                                                                                                                                    |

|    | T             | $\bigcap$ |              |                 |                                                                                                                                                                    |

| 65 | 9             | <br>/3    | 0000         |                 | Unset indicator 13                                                                                                                                                 |

An example of a test instruction for indicator 15 is shown in Figure 6.

### Manual Indicators 20 to 29

2.10.14

There are ten manual indicators, i.e. 20 to 29, which are all identical in operation. These indicators are set and unset by means of manual controls (switches) on the console display panel, the operation of one of these switches causing its corresponding indicator to be set or unset. The indicator will remain set until it is unset by operation of the appropriate switch, i.e. its state is unaffected by test instructions.

The manual indicators are intended for use in applications where it is desired to make minor alterations to a program without recourse to reading in a different program.

**Example** In a payroll application a manual indicator could effect a change-over from weekly to monthly payroll, the indicator being used to modify the program in such a way that the appropriate monthly tax constants would be used instead of weekly constants during the P.A.Y.E. calculations.

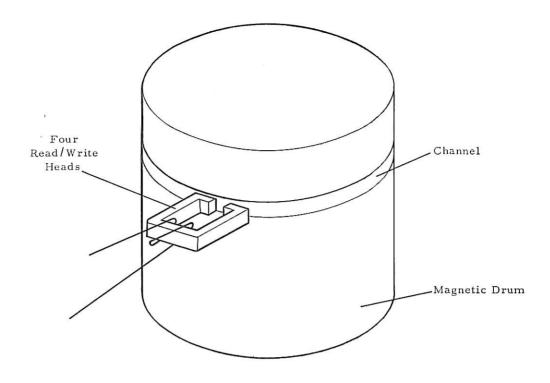

Figure 9: MAGNETIC DRUM

#### THE MAGNETIC DRUM

2.11

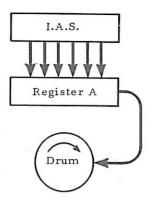

The magnetic drum is a backing store for the computer. Program instructions cannot be obeyed from the drum and the drum cannot be addressed directly other than to effect a transfer to or from I.A.S. Program instructions are provided for executing drum transfers.

The drum store is much larger than I.A.S. and it is therefore usual to hold the bulk of information on the drum and to transfer the information to I.A.S. as it is required. However, access to the drum is time consuming and the program should be arranged so that drum transfers are kept to a minimum.

A standard drum has 12,000 storage locations. A computer may be fitted with a quarter drum of 3,000 words, a half drum of 6,000 words, or one or more standard drums up to a maximum of eight drums.

Each 12,000 word drum is divided into two sections of 6,000 words and for timing purposes is regarded as being two separate drums. There are no such divisions on the 3,000 word drums or the 6,000 word drums.

The drum (Figure 9) is divided along its length into channels. A series of read/write heads are positioned along the length of the drum for transferring information to and from each channel. Each channel contains 200 words divided into groups of 10 words each called decades. The drum rotates at a constant speed, the locations moving in sequence past the read/write heads.

The decade is the smallest unit of transfer possible. In a drum transfer instruction, the drum address specified is a decade address. The largest unit which can be transferred by one instruction is 20 decades. It is possible to effect drum transfers either as a specified number of decades or as a complete channel. If the transfer is more than one decade, then it is possible for the decades to be taken from two separate channels provided that the decade numbering sequence is not broken.

The decade addresses of locations on the drum are shown in the table below.

| Words  | Drum Number | Decade Addresses |

|--------|-------------|------------------|

| 3,000  | 1           | 0000 to 0299     |

| 6, ɗoo | 1           | 0000 to 0599     |

| 12,000 | 1           | 0000 to 1199     |

| 12,000 | 2           | 1200 to 2399     |

| 12,000 | 3           | 2400 to 3599     |

| 12,000 | 4           | 3600 to 4799     |

| 12,000 | 5           | 4800 to 5999     |

| 12,000 | 6           | 6000 to 7199     |

| 12,000 | 7           | 7200 to 8399     |

| 12,000 | 8           | 8400 to 9599     |

| 1      |             |                  |

DECADE ADDRESSES OF 3,000, 6,000 AND 12,000 WORD DRUMS

If an address outside the range for any machine is specified in an instruction, the machine will stop due to failure to synchronize the clock source and the Slip Pulse lamp will glow.

The gap between decades is one word length and channel switching (i.e. when transferring decades from the end of one channel and the beginning of the next) occurs while this gap is passing the read/write heads.

**Example** Decades 59 and 60 (i.e. the last decade of one channel and the first decade of the next) are to be transferred. The transfer will be completed 21 word times after the start of the transfer of the first word of decade 59.

It is apparent that when transferring a specified number of decades the transfer time is the same irrespective of whether the transfer extends over one or two channels. This rule does not apply however when switching from the last decade of the first drum section to the first decade of the second drum section or when channel switching between drums.

Switching between drums or switching between drum sections takes up to just over one drum revolution.

Example 1 If decades 1199 and 1200 (i.e. the last decade of drum number 1 and the first decade of drum number 2) are transferred, then, on completion of the transfer of decade 1199, the transfer stops until the central processor is clocked by the second drum. This may take up to just over one drum revolution time. When the computer is clocked, decade 1200 is positioned at the read/write heads and the second transfer is effected.

Example 2 If decades 599 and 600 (i.e. the last decade of the first drum section and the first decade of the second drum section) are transferred, then, on completion of the transfer of decade 599, the transfer stops until the central processor is clocked by the second section. This may take up to just over one drum revolution time. When the computer is clocked, decade 600 is positioned at the read/write heads and the second transfer is effected.

In the two examples given, the maximum time taken for transfer of the two decades is a normal access time, plus a little over one drum revolution clocking time, plus the normal transfer time for two decades. The clock generator of the central processor is synchronized either by the drum or drum section currently in use, or by the drum or drum section to which reference was last made.

The arrangements referred to in the preceding paragraphs are dealt with completely automatically within the computer. It is only necessary to take note of these times under special circumstances which involve time-sharing of the central processor between drum references and input or output equipment.

In addition to the storage quoted for each drum, there are a further two channels (i.e. 400 locations) of reserved storage. On the first drum of each machine the reserved storage holds the Initial Orders program and engineer's Test Routines. The reserved storage is not accessible to the programmer for transfers from I.A.S. though transfers to I.A.S. from the reserved channels are permissible.

Drum Instructions 2.11.1

All transfer instructions from and to the drum are double-length and occupy all twelve digits of a storage location. There are two types of transfers; decade transfers and channel transfers. The functions are 80 to 87; functions 84 to 87 involve the use of the reserved store.

Function 80 2.11.2

Effect Transfers the contents of a specified number of decades of I.A.S. to the drum.

Operation The first location of I.A.S. from which the transfer is made is that specified in the instruction, successive transfers being from successively higher numbered locations of I.A.S. The information is taken from I.A.S. and is placed in Register A before being written on the drum. The first location of the drum to which the transfer is to be made is the first location of the drum decade specified in the instruction, successive locations being transferred to the second, third ... tenth locations of that decade followed by the first, second, third ....tenth locations of successively higher numbered decades. The contents of I.A.S. remain unaltered.

Example The contents of I.A.S. locations 249 to 388 (i.e. 14 decades starting from location 249) are to be transferred to decades 0805 to 0818 on the drum.

| Instructions | ı | D | F  | Α    | R |

|--------------|---|---|----|------|---|

|              | ¥ |   | 90 | 0249 | _ |

|              | ^ |   | 14 | 0805 | _ |

### Function 8

2.11.3

Effect Transfers the contents of a specified number of drum decades to I.A.S.

Operation The first location of the drum from which the transfer is made is that specified in the instruction, successive transfers being from the second, third....tenth location of that decade followed by the first, second, third....tenth locations of successively higher numbered decades. The information is taken from the drum and is placed in Register A before being written into I.A.S. The first location of I.A.S. to which the transfer is to be made is the first location of I.A.S. specified in the instruction, successive transfers being to successively higher numbered location of I.A.S. The contents of the drum remain unaltered.

Example The contents of drum decades 0805 to 0818 (i.e. 140 words starting from decade 0805) are to be transferred to I.A.S. locations 249 to 388.

Function 82 2.11.4

Effect Transfers the contents of 200 locations of I.A.S. to a specified channel on the drum.

Operation The first location of I.A.S. from which the transfer is made must be a multiple of 200, i.e. 0000, 0200, 0400..... or 3800. Successive words are transferred from successively higher numbered locations of I.A.S. The information is routed through Register A. The drum address specified in the instruction is the lowest numbered decade of the channel to which the transfer is to be made. The transfer begins at the start of the first decade to reach the read/write heads. This means that if I.A.S. locations 0 to 199 are to be transferred to drum decades 60 to 79 and drum decade 74 is the first decade to reach the read/write heads, then; I.A.S. word 140 is transferred to the first location of drum decade 74 followed in sequence by words 141, 142 .....199, 0, 1, 2..... to 139. The drum decades will be filled in the sequence 74, 75 ..... 79, 60, 61 .... to 73.

Example The contents of I.A.S. locations 200 to 399 are to be transferred to the 32nd channel on the drum (i.e. decades 0620 to 0639).

Function 83 2.11.5

Effect Transfers the contents of a specified channel of the drum to 200 locations of I.A.S.

Operation As with function 82, the I.A.S. address must be 0000, 0200, 0400, ...or 3800. Also, the drum address specified in the instruction is the lowest numbered decade of the channel from which the transfer is made. The transfer begins with the first location of the first decade to reach the read/write heads.

Example The contents of the 50th channel of the drum (i.e. decades 0980 to 0999) are to be transferred to locations 0800 to 0999 of I.A.S.

Note on Functions 82 and 83 If two channel transfers are succeeding instructions, then the access time for the second channel transfer will be zero provided that both the transfers are to or from the same drum or to or from the same drum section on 12,000 word drums.

Reserved Storage 2.11.6

As stated in 2.11, there are two additional channels of reserved storage on each drum from which the programmer may transfer information or instructions to I.A.S., but to which the programmer can only transfer from I.A.S. if an engineer's adjustment is made to the computer.

On the first drum, part of this storage is used to hold the Initial Orders program of instructions, which could be mutilated accidentally unless there was some restriction placed on its use by the programmer.

This storage is decade addressed as follows:-

- (a) 0000 to 0019 plus 1200 (n 1) where n is the number of the drum and

- (b) 0100 to 0119 plus 1200 (n 1)  $\int n = 1$  for 3,000 word and 6,000 word drums.

It will be appreciated that these addresses are also decade addresses of the 'free' storage on each drum, the distinction being drawn by the computer according to the function codes used. Functions 84, 85, 86 and 87 are used when transferring information or instructions to or from the reserved channels.

If any of these functions is used in such a way that the drum address in the instruction is outside the specifiable address range for any of the reserved channels then the transfer will be made to or from the address specified in free storage on the drums.

Function 84 2.11.7

Effect Transfers the contents of a specified number of decades of I.A.S. to the reserved channels of the drum.

Operation Similar to function 80, but can only be accomplished with the assistance of the engineer and has restricted use.

Example The contents of locations 129 to 248 of I.A.S. are to be transferred to decades 0102 to 0113 of reserved storage on the first drum.

Instruction

Similar to function 81.

|   | D | F  | A    | R |

|---|---|----|------|---|

| × | _ | 84 | 0129 |   |

|   |   | 12 | 0102 | _ |

Function 85

Operation

2.11.8

Effect Transfers the contents of a specified number of decades of drum reserved storage to I.A.S.

Example The contents of decades 0004 to 0012 of reserved storage on the first drum are to be transferred to locations 0302 to 0391 of I.A.S.

Instruction

|   | D | F  | A    | R |

|---|---|----|------|---|

| × | _ | 85 | 0302 |   |

|   |   | 09 | 0004 |   |

Function 86

2.11.9

Effect Transfers the contents of 200 locations of I.A.S. to one of the reserved channels of the drum.

Operation Similar to function 82 but can only be accomplished with the assistance of the engineer and has restricted use.

Example The contents of location 1200 to 1399 of I.A.S. are to be transferred to the second reserved channel of the third drum.

Instruction

| I | D | F  | A    | R |

|---|---|----|------|---|

| X |   | 86 | 1200 |   |

| • |   | 20 | 2500 | - |

Function 87

2.11.10

Effect Transfers the contents of a reserved channel of the drum to 200 locations of I.A.S.

Operation Similar to function 83.

**Example** The contents of the first reserved channel of the fifth drum are to be transferred to locations 1800 to 1999 of I.A.S.

Instruction

|   | D | F  | Α    | R |

|---|---|----|------|---|

| × |   | 87 | /800 |   |

|   |   | 20 | 4800 | - |

#### Relative Addressing of Drum Instructions

2.11.11

The drum instructions have been explained using absolute addresses. Relative addresses can be used, in which case the I.A.S. address and the drum decade address can refer to the same, or to different relativizers. The appropriate relativizer reference number must be placed in each half of the double-length instruction.

Example If R.R.N. 15 has an I.A.S. address of 800 and a drum location address of 9800, the instruction

|   | D | F  | Α  | R  |

|---|---|----|----|----|

| × |   | 83 | 00 | 15 |

|   |   | 20 | 0  | 15 |

will be obeyed in the same way as

|   | D | F  | A    | R |

|---|---|----|------|---|

| × |   | 83 | 0800 |   |

|   |   | 20 | 0980 | 1 |

and the contents of the 50th channel of the drum (decades 980 to 999) will be transferred to locations 800 to 999 of I.A.S.

Example If R.R.N. 17 has an I.A.S. address of 240 and a drum location address of 5000, and R.R.N. 18 has an I.A.S. address of 360 and a drum location address of 8000 the instruction

|   | D | F  | A | R  |

|---|---|----|---|----|

| × |   | 81 | 9 | 17 |

|   |   | 14 | 5 | 18 |

will be obeyed in the same way as

| 1 | D | F   | A    | R |

|---|---|-----|------|---|

| × |   | 81  | 0249 |   |

|   |   | 14- | 0805 | _ |

and the contents of drum decades 0805 to 0818 will be transferred to I.A.S. locations 249 to 388.

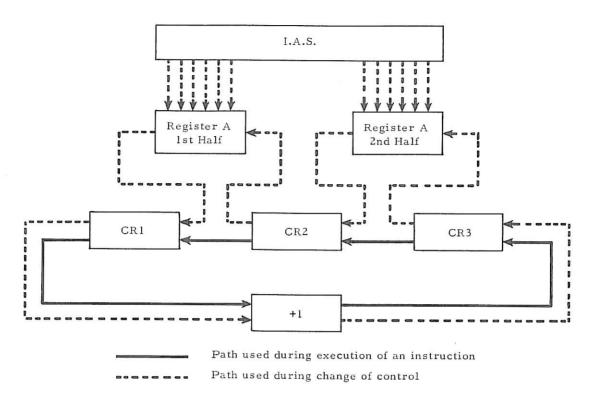

#### THE CONTROL REGISTERS

2.12

Instructions are normally obeyed in the sequential order in which they are stored in I.A.S. Instructions are transferred from I.A.S. by way of Register A to the control registers before being obeyed.

There are three control registers CR1, CR2 and CR3, each six digits in length and therefore capable of holding one single-length instruction apiece. The circuitry of the control registers is so arranged that after the second instruction in a word has been obeyed, control is transferred automatically to the first instruction of the next word. This sequence is broken only when a programmed jump occurs.

An instruction is actually obeyed when the instruction is in CR1. Figure 10 shows two transfer paths, one for an instruction other than a jump instruction and the other for a jump instruction. The sequence of operations for each instruction is as follows:

- (a) An instruction other than an indicator test entering CR1 is obeyed. The contents of CR3 move into CR2, the previous contents of CR2 move into CR1 and the previous contents of CR1 have one added in the least-significant position before being moved into CR3.

- (b) When an indicator test enters CR1 and is unsuccessful, then the transfer sequence is as follows:

- (i) The contents of the first half of the I.A.S. location specified in the instruction are transferred to the second half of Register A; the first half of Register A will contain zeros in all six positions.

- (ii) The contents of CR3 move into CR2, the previous contents of CR2 move into CR1 and the previous contents of CR1 have one added in the least-significant position before being moved into CR3.

- (c) When an indicator test instruction enters CR1 and is successful, a change of control takes place and the transfer sequence is as follows:

- (i) The contents of the I.A.S. location in the address part of the instruction are moved from I.A.S. into Register A.